Delay(1200); // >= 200us

Delay(60000); // >= 10ms

Delay(180000); // >= 30ms

Delay(240000); // >= 40ms

Delay(300000); // >= 50ms

Delay(420000); // >= 70ms

2009년 10월 14일 수요일

2009년 10월 11일 일요일

Configuration of COM26T2844VTX color LCD in STR91x

* CPU IF (9bit data bus)

- 2 cycle transfer through 9bit data bus

- assignment

DB17,DB16,DB15,DB14,DB13,DB12,DB11,DB10,DB9

R5, R4, R3, R2, R1, R0, G5, G4, G3

G2, G1, G0, B5, B4, B3, B2, B1, B0

- IM3-0(system interface selection)

IM3 IM2 IM1 IM0

1010 -> 80-system 18bit interface

0010 -> 80-system 16bit interface

0011 -> 80-system 8bit interface

1011 -> 80-system 9bit interface

- registers

IR : 16bit index register

WDR : 18bit write-data register

RDR : 18bit read-data register

- register selection(parallel interface)

WRB RDB RS

010 -> Write index of IR

100 -> Setting disabled

011 -> write to a control register and internal GRAM via WDR

101 -> Read from the internal GRAM via the RDR

- 2 cycle transfer through 9bit data bus

- assignment

DB17,DB16,DB15,DB14,DB13,DB12,DB11,DB10,DB9

R5, R4, R3, R2, R1, R0, G5, G4, G3

G2, G1, G0, B5, B4, B3, B2, B1, B0

- IM3-0(system interface selection)

IM3 IM2 IM1 IM0

1010 -> 80-system 18bit interface

0010 -> 80-system 16bit interface

0011 -> 80-system 8bit interface

1011 -> 80-system 9bit interface

- registers

IR : 16bit index register

WDR : 18bit write-data register

RDR : 18bit read-data register

- register selection(parallel interface)

WRB RDB RS

010 -> Write index of IR

100 -> Setting disabled

011 -> write to a control register and internal GRAM via WDR

101 -> Read from the internal GRAM via the RDR

라벨:

embedded system

usage str91x pins

*******************************

* Pin ** ALT ****** Descript **

*******************************

* P2.4 * ALT_OUT2 * SSP0_SCLK *

* P2.5 * ALT_OUT3 * SSP0_MOSI *

* P2.6 * ALT_IN1 ** SSP0_MISO *

* P2.7 * ALT_OUT2 * SSP0_NSS **

---- SD Card Connection -------

* P3.0 * ALT_IN1 ** UART0_Rxd *

* P3.1 * ALT_OUT2 * UART0_TX **

- Serial Terminal Connection --

* P3.2 * ALT_IN1 ** UART1_Rxd *

* P3.3 * ALT_OUT2 * UART1_TX **

--- GPS Module Connection -----

* P3.4 * ALT_OUT2 * SSP1_SCLK *

* P3.5 * ALT_IN1 ** SSP1_MISO *

* P3.6 * ALT_OUT2 * SSP1_MOSI *

* P3.7 * ALT_OUT2 * SSP1_NSS **

-- TLV320AIC261 Connection ----

* P4.x -> general ADC(touch panel)

* P7.[0:5] -> [RELEASE,CSB,RS,WRB,RDB,RESTB]

* P8.x -> DB1..8

* p9.x -> DB9..17

--- LCD connnection -----------

* Pin ** ALT ****** Descript **

*******************************

* P2.4 * ALT_OUT2 * SSP0_SCLK *

* P2.5 * ALT_OUT3 * SSP0_MOSI *

* P2.6 * ALT_IN1 ** SSP0_MISO *

* P2.7 * ALT_OUT2 * SSP0_NSS **

---- SD Card Connection -------

* P3.0 * ALT_IN1 ** UART0_Rxd *

* P3.1 * ALT_OUT2 * UART0_TX **

- Serial Terminal Connection --

* P3.2 * ALT_IN1 ** UART1_Rxd *

* P3.3 * ALT_OUT2 * UART1_TX **

--- GPS Module Connection -----

* P3.4 * ALT_OUT2 * SSP1_SCLK *

* P3.5 * ALT_IN1 ** SSP1_MISO *

* P3.6 * ALT_OUT2 * SSP1_MOSI *

* P3.7 * ALT_OUT2 * SSP1_NSS **

-- TLV320AIC261 Connection ----

* P4.x -> general ADC(touch panel)

* P7.[0:5] -> [RELEASE,CSB,RS,WRB,RDB,RESTB]

* P8.x -> DB1..8

* p9.x -> DB9..17

--- LCD connnection -----------

라벨:

embedded system

2009년 10월 8일 목요일

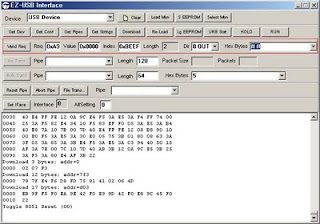

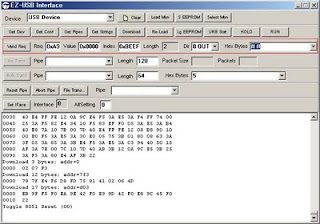

Rewriting broken EEPROM of Cypress FX2 (non 0xFFFF in first word)

1. plugg off USB connection or Power Supply in FX2 board.

2. remove the boot EEPROM from FX2 board.

3. plugg on USB connection and Power Supply in FX2 board.

4. Carefully attach the boot EEPROM on same place of FX2 board to sustain USB connection and Power suppling.

5. Downloading C:\Cypress\USB\Examples\FX2LP\Vend_ax\Vend_Ax.hex using Cyconsol.exe.

6. Click "Vend Req" with the below picture.

7. Push reset button of FX2 board.

8. verify the device name "USB Device".

2. remove the boot EEPROM from FX2 board.

3. plugg on USB connection and Power Supply in FX2 board.

4. Carefully attach the boot EEPROM on same place of FX2 board to sustain USB connection and Power suppling.

5. Downloading C:\Cypress\USB\Examples\FX2LP\Vend_ax\Vend_Ax.hex using Cyconsol.exe.

6. Click "Vend Req" with the below picture.

7. Push reset button of FX2 board.

8. verify the device name "USB Device".

라벨:

embedded system

2009년 10월 7일 수요일

2009년 10월 5일 월요일

fpga의 신호선 설계정책

입력과 출력은 빵빵하게 버퍼(IBUF, OBUF)를 사용하고

무엇보다도 클럭은 정교하고 안정적이도록 dcm을 꼭 사용하자 IP coregen을 이용해서

무엇보다도 클럭은 정교하고 안정적이도록 dcm을 꼭 사용하자 IP coregen을 이용해서

라벨:

embedded system

2009년 10월 3일 토요일

Useful schematic library of STR91XFWQ 128-pin LQFP in KiCad

EESchema-LIBRARY Version 2.3 Date: 2009-10-03 오전 11:18:32

#

# STR91XFWA

#

DEF STR91XFWA U 0 40 Y Y 1 F N

F0 "U" 0 -550 60 H V C CNN

F1 "STR91XFWA" 0 50 60 H V C CNN

DRAW

S -950 950 1000 -1000 0 0 0 N

T 0 0 -50 60 0 0 0 128-pin~LQFP Normal 0

X P4.3 128 -750 1100 147 D 28 28 1 1 B

X P4.4 127 -700 1100 147 D 28 28 1 1 B

X P4.5 126 -650 1100 147 D 28 28 1 1 B

X P4.6 125 -600 1100 147 D 28 28 1 1 B

X P4.7 124 -550 1100 147 D 28 28 1 1 B

X AVREF 123 -500 1100 147 D 28 28 1 1 W

X AVDD 122 -450 1100 147 D 28 28 1 1 W

X VSSQ 121 -400 1100 147 D 28 28 1 1 W

X VDDQ 120 -350 1100 147 D 28 28 1 1 W

X P7.7 119 -300 1100 147 D 28 28 1 1 B

X P7.6 118 -250 1100 147 D 28 28 1 1 B

X JTDO 117 -200 1100 147 D 28 28 1 1 B

X P1.7 116 -150 1100 147 D 28 28 1 1 B

X JTDI 115 -100 1100 147 D 28 28 1 1 B

X P1.6 114 -50 1100 147 D 28 28 1 1 B

X VSS 113 0 1100 147 D 28 28 1 1 W

X VDD 112 50 1100 147 D 28 28 1 1 W

X JTMS 111 100 1100 147 D 28 28 1 1 B

X P1.5 110 150 1100 147 D 28 28 1 1 B

X P1.4 109 200 1100 147 D 28 28 1 1 B

X JTCK 108 250 1100 147 D 28 28 1 1 B

X JTRSTn 107 300 1100 147 D 28 28 1 1 B

X P1.3 106 350 1100 147 D 28 28 1 1 B

X VSSQ 105 400 1100 147 D 28 28 1 1 W

X X1_CPU 104 450 1100 147 D 28 28 1 1 B

X X2_CPU 103 500 1100 147 D 28 28 1 1 B

X VDDQ 102 550 1100 147 D 28 28 1 1 W

X P1.2 101 600 1100 147 D 28 28 1 1 B

X RESET_OUTn 100 650 1100 147 D 28 28 1 1 O

X P1.1 99 700 1100 147 D 28 28 1 1 B

X P1.0 98 750 1100 147 D 28 28 1 1 B

X JRTCK 97 800 1100 147 D 28 28 1 1 B

X P3.5 65 1150 -800 147 L 28 28 1 1 B

X P3.6 66 1150 -750 147 L 28 28 1 1 B

X P0.0 67 1150 -700 147 L 28 28 1 1 B

X P3.7 68 1150 -650 147 L 28 28 1 1 B

X P0.1 69 1150 -600 147 L 28 28 1 1 B

X P5.4 70 1150 -550 147 L 28 28 1 1 B

X P0.2 71 1150 -500 147 L 28 28 1 1 B

X VSSQ 72 1150 -450 147 L 28 28 1 1 W

X VDDQ 73 1150 -400 147 L 28 28 1 1 W

X EMI_ALE 74 1150 -350 147 L 28 28 1 1 B

X EMI_RDn 75 1150 -300 147 L 28 28 1 1 B

X P0.3 76 1150 -250 147 L 28 28 1 1 B

X P5.5 77 1150 -200 147 L 28 28 1 1 B

X P0.4 78 1150 -150 147 L 28 28 1 1 B

X P5.6 79 1150 -100 147 L 28 28 1 1 B

X P5.7 80 1150 -50 147 L 28 28 1 1 B

X VDD 81 1150 0 147 L 28 28 1 1 W

X VSS 82 1150 50 147 L 28 28 1 1 W

X P6.4 83 1150 100 147 L 28 28 1 1 B

X P6.5 84 1150 150 147 L 28 28 1 1 B

X P0.5 85 1150 200 147 L 28 28 1 1 B

X VDDQ 86 1150 250 147 L 28 28 1 1 W

X VSSQ 87 1150 300 147 L 28 28 1 1 W

X P0.6 88 1150 350 147 L 28 28 1 1 B

X RESET_INn 89 1150 400 147 L 28 28 1 1 I

X P0.7 90 1150 450 147 L 28 28 1 1 B

X TAMPER_IN 91 1150 500 147 L 28 28 1 1 I

X P6.6 92 1150 550 147 L 28 28 1 1 B

X P6.7 93 1150 600 147 L 28 28 1 1 B

X MII_MDIO 94 1150 650 147 L 28 28 1 1 B

X USBDN 95 1150 700 147 L 28 28 1 1 B

X USBDP 96 1150 750 147 L 28 28 1 1 B

X P8.3 32 -1100 -800 147 R 28 28 1 1 B

X P6.1 31 -1100 -750 147 R 28 28 1 1 B

X P8.2 30 -1100 -700 147 R 28 28 1 1 B

X P6.0 29 -1100 -650 147 R 28 28 1 1 B

X P8.1 28 -1100 -600 147 R 28 28 1 1 B

X P5.3 27 -1100 -550 147 R 28 28 1 1 B

X P8.0 26 -1100 -500 147 R 28 28 1 1 B

X PHYCLK/P5.2 25 -1100 -450 147 R 28 28 1 1 B

X VSSQ 24 -1100 -400 147 R 28 28 1 1 W

X VDDQ 23 -1100 -350 147 R 28 28 1 1 W

X EMI_WRHn 22 -1100 -300 147 R 28 28 1 1 O

X EMI_BWR_WRLn 21 -1100 -250 147 R 28 28 1 1 O

X P5.3 20 -1100 -200 147 R 28 28 1 1 B

X P5.2 19 -1100 -150 147 R 28 28 1 1 B

X P5.1 18 -1100 -100 147 R 28 28 1 1 B

X VDD 17 -1100 -50 147 R 28 28 1 1 W

X VSS 16 -1100 0 147 R 28 28 1 1 W

X P7.5 15 -1100 50 147 R 28 28 1 1 B

X P7.4 14 -1100 100 147 R 28 28 1 1 B

X P7.3 13 -1100 150 147 R 28 28 1 1 B

X P5.0 12 -1100 200 147 R 28 28 1 1 B

X P2.1 11 -1100 250 147 R 28 28 1 1 B

X P2.0 10 -1100 300 147 R 28 28 1 1 B

X VDDQ 9 -1100 350 147 R 28 28 1 1 B

X VSSQ 8 -1100 400 147 R 28 28 1 1 B

X P7.2 7 -1100 450 147 R 28 28 1 1 B

X P7.1 6 -1100 500 147 R 28 28 1 1 B

X P7.0 5 -1100 550 147 R 28 28 1 1 B

X AVSS 4 -1100 600 147 R 28 28 1 1 W

X P4.0 3 -1100 650 147 R 28 28 1 1 B

X P4.1 2 -1100 700 147 R 28 28 1 1 B

X P4.2 1 -1100 750 147 R 28 28 1 1 B

X P2.2 33 -750 -1150 147 U 28 28 1 1 B

X P8.2 34 -700 -1150 147 U 28 28 1 1 B

X P2.3 35 -650 -1150 147 U 28 28 1 1 B

X P8.5 36 -600 -1150 147 U 28 28 1 1 B

X P2.4 37 -550 -1150 147 U 28 28 1 1 B

X P8.6 38 -500 -1150 147 U 28 28 1 1 B

X VBATT 39 -450 -1150 147 U 28 28 1 1 W

X VSSQ 40 -400 -1150 147 U 28 28 1 1 W

X X2_RTC 41 -350 -1150 147 U 28 28 1 1 B

X X1_RTC 42 -300 -1150 147 U 28 28 1 1 B

X VDDQ 43 -250 -1150 147 U 28 28 1 1 W

X P8.7 44 -200 -1150 147 U 28 28 1 1 B

X P2.5 45 -150 -1150 147 U 28 28 1 1 B

X P9.0 46 -100 -1150 147 U 28 28 1 1 B

X P9.1 47 -50 -1150 147 U 28 28 1 1 B

X VSS 48 0 -1150 147 U 28 28 1 1 W

X VDD 49 50 -1150 147 U 28 28 1 1 W

X P9.2 50 100 -1150 147 U 28 28 1 1 B

X P9.3 51 150 -1150 147 U 28 28 1 1 B

X P9.4 52 200 -1150 147 U 28 28 1 1 B

X P2.6 53 250 -1150 147 U 28 28 1 1 B

X USBCLK/P2.7 54 300 -1150 147 U 28 28 1 1 B

X P3.0 55 350 -1150 147 U 28 28 1 1 B

X VSSQ 56 400 -1150 147 U 28 28 1 1 W

X VDDQ 57 450 -1150 147 U 28 28 1 1 W

X P9.5 58 500 -1150 147 U 28 28 1 1 B

X P3.1 59 550 -1150 147 U 28 28 1 1 B

X P3.2 60 600 -1150 147 U 28 28 1 1 B

X P3.3 61 650 -1150 147 U 28 28 1 1 B

X P9.6 62 700 -1150 147 U 28 28 1 1 B

X P3.4 63 750 -1150 147 U 28 28 1 1 B

X P9.7 64 800 -1150 147 U 28 28 1 1 B

ENDDRAW

ENDDEF

#

#End Library

라벨:

schematics

2009년 10월 2일 금요일

change ~~~.... windows to linux

IE -> firefox

Visual Studio -> Eclipse

Orcad -> Kicad

Keil -> SDCC

above all, try to Virtual Box as the bridge to complete linux machine.

Visual Studio -> Eclipse

Orcad -> Kicad

Keil -> SDCC

above all, try to Virtual Box as the bridge to complete linux machine.

피드 구독하기:

글 (Atom)