그래서 구조적으로 견고하고 일정한 반경의 돔을 간단한 기초 작업으로 쉽게 만드는 방법을 찾던 중 pentagon(5각형)으로 암실 돔을 구성하면 어떨까? 하고 찾아 보았다. 외국에서는 과학 캠프나 실습차원에서 많이 하는 것 같다. 나도 예전에 서울 대공원에서 본 것 같은 기억이 있다. 가본지 너무 오래 되어서 아마도 거기 입장료가 좀 쎘었던거 같다.

아무튼 http://hilaroad.com/camp/projects/dome/domemath.html 에 가보면 원하는 직경의 Geodesic 돔을 구성할 수 있는 계산을 할 수 있게 해준다. 다음에는 이것을 번역해 보아야 겠다. 위와 같은 것을 레고 처럼 구성할 수 있다면 조명과 카메라를 자유 자재로 안정적인 위치에 고정 시킬 수 있을 거 같다.

Hila Science Camp

Dome Math

Geodesic Domes

돔을 만드는 사람들은 이러한 방식의 돔을 2V Icosa Alternate 라고 부른다. icosahedron의 각 삼각형 표면안에 딱 맞는 4개의 삼각형에 의해서 만들어 진다. icosahedron란 뭔가? icosahedron는 고대 그리스인들에 의해서 만들어진 5개의 구조물(solids) 중의 하나이다. 이것이 그들 5개이다:

어떻게 이름 지어졌을까? 우측 맨 끝이 icosahedron이다. 이것은 20의 삼각형 면을 가지고 있다.

여러분이 정말로 정말로 알고 싶다면, 다음의 링크를 따라가서 어떻게 삼각형이 icosahedron의 각각의 삼각형에 맞아 떨어지는지 알아 볼 수 있다. - Icosahedron Domes Explained!

맨 위에서 보여주는 것과 같은 돔을 만들기 위해서, 여러분은 40개의 삼각형, 30개의 isosceles 삼각형, 그리고 10 equilateral 삼각형을 만들어야 한다.

돔을 디자인해 봅시다!

1단계:

여러분이 만들고자하는 돔의 직경을 결정하자. 우선 작은 30cm정도의 직경을 갖는 작은 모델을 만들어 보자.

2단계:

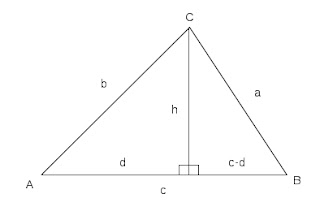

필요한 삼각형의 크기를 결정하자. 우리가 만들어야할 삼각형은 각면에 접착용 탭이 필요하다. 다음과 같이 생겼다:

10개의equilateral 삼각형은 각 면이 "A" 길이로 같다. "A"를 결정하기 위해서 "Chord Factor" 라고 불리는 숫자를 사용한다.

"A"를 위한 chord factor는 0.61803. "A"의 길이를 결정하기 위해서 여러분이 디자인한 돔의 반경에 이 chord factor를 곱하자. 반경은 직격의 1/2에 해당한다는 것을 잊지 말자. 지금 디자인하는 돔은 직경이 30cm이고 반경은 15cm이다.

A = 15 cm x 0.61803

A = 9.27045 cm

A=9.27 cm

B = 15 cm x 0.54653

B = 8.19795 cm

B = 8.20 cm

3단계:

이 돔을 구성하기 위해서 "A"와 "B"값으로 구성된 삼각형 요소들을 만들어야 한다. 단단한 cardboard위에 30cm 직경의 원을 그리고 다음 링크의 내용을 따라하도록 하자. instructions for constructing the 50 cm dome.어떤 크기의 돔이라도 만들 수 있다. 그저 반경에 chord factor만 곱하면 된다. 그리고 나서 조립하는 순서만 따라하면 된다.

이 페이지는 Hila Science Camp: http://hilaroad.com 에 의해서 만들어 졌습니다.

돔 조립하기

Geodesic dome들은 우아하고 정교한 구조물이다. 가벼운 무게와 강인함으로 인해서 재료를 아주 효율적으로 사용하도록 만든다. 북극과 같은 먼 지역에서 사용하기에 이상적인 구조다. 언젠가 달이나 covering(?) 도시에서 돔 구조물을 볼지도 모른다.

이 사이트는 종이로 geodesic dome을 만드는 과정을 차례차례로 제공한다. 그 내용은 다른 크기의 dome을 디자인할 수 있는 것도 포함한다.

이 프로젝트는 많은 지방과 주에서의 과학과 기술 교과 과정의 구조와 매커니즘 부분을 지원한다. 교과 과정의 목표는 geodesic dome이나 shell 구조물을 구축하는 것을 종종 포함한다. geodesic dome은 독특한 구조에서 생기는 응측력과 팽창력을 보여준다. 여러분은 다양한 재질로된 geodesic dome을 구축할 수 있다. 지금의 dome은 종이로 구축될 것이다. 다른 크기의 dome을 구축하기 위해선 여기서 제시된 디자인 개념을 사용하고 Bristol 보드나 골판지, plywood 심지어는 얼음과 같은 재료로도 도전해 보자!

6, 7 학년의 학생에 대해서 어떤 교사들은 활기차고 화려한 조작으로 변화 시켜서 이 같은 활동을 미술 시간과 결합하기도 한다.

이 프로젝트의 수학적인 부분은 8학년과 9학년의 응용 수학에 아주 적당하다. 응용 수학과 "구조와 매커니즘"에 대한 여러분의 주와 지방의 교과 과정 문서를 확인해보자.

Geodesic Dome 구축하기

Geodesic dome은 Buckminister Fuller에 의해서 대중화 되고 삼각형들의 구조적 접목이 dome이나 shell 구조물의 고유의 강도에 더해 졌다.

다음은 50cm의 직경을 갖는 geodesic dome의 구축하는데 필요한 지시사항들이다. 여러분이 다른 크기의 dome을 만들고자 한다면 다음 링크를 따라하자. - DOME MATH

먼저 아래에 보여진 삼각형들의 정확한 그림을 생성해서 시작해보자. 여러분은 30개의 B-A-B 삼각형과 10개의 A-A-A 삼각형이 필요하다. 이 삼각형으로 만들어진 유닛들은 기본 구성 요소가 된다. 여러분은 이 삼각형들을 정확하기 만들어야 하기 때문에 제시된 수치들은 매우 중요하다. 콤파스와 자를 사용하자. A, B의 수치는 삼각형의 각 면의 길이가 되고 접착면을 위한 tab은 여분이 됨을 주의하자.

A-A-A 삼각혀은 equilateral 이라고 하고, B-A-B 삼각형은 isosceles라고 한다.

이것은 기하학에서 훌룡한 예제가 된다. 각 삼각형의 요소요소의 정확한 도면을 만들기 위해서 콤파스와 자, 연필로 작업하자.

각 삼각형의 도면을 그린 후 photo copy만으로 dome을 만드는데 충분하다. 어떤 종류의 종이도 적당하다.

두 가지 색상의 종이를 사용하자. 하나는 A-A-A 삼각형에, 다른 하나는 B-A-B 삼각형에 사용하자. 색상을 다르게 하는 것은 구축을 쉽게하고 여러분의 dome을 좀 더 극적이게 보이도록 만든다.

나는 이 삼각형들의 도면을 그리고 싶지 않다. 그져 dome을 만들고 싶다!

좋다. 이미 그려진 요소들을 위한 프린트 가능한 페이지에 대한 링크를 따라가라.

Link to template for A-A-A triangle: (PDF File)

Link to template for B-A-B triangle: (PDF File)

주의 사항: 프린트 한후 "A"와 "B"면이 정확한 길이로 프린트 되었는지 확인하라. 모든 프린트가 동일한 해상도 이지는 않다.

삼각형을 잘라내고 tab 라인을 조심스럽게 접자. 깔끔하게 접는 것이 무엇보다도 중요하다.

다섯개의 A-B-B삼각형을 조합해서 pentagon을 만들자. "B"면을 접착면을 활용해서 접착시키자. 접착용 풀은 이 프로젝트에 아주 적당하다.

pentagon의 외부 면이 삼각형의 "A" 면이 되도록하는 것을 명심하자.

완성된 pentagon은 위의 이미지와 같게 보여야 한다. 가운데가 쏫아 올라와야 한다. 다섯개의 pentagon을 더 만들자.

판지로 75cm 직경의 원은 만들어서 dome을 위한 바닥을 만들자.

그리고 그 바닥의 중앙에 50cm 직경의 원은 그리자.

바닥의 중앙의 25cm의 원을 잘라내자. 이것은 dome의 안쪽을 접근할 수 있도록 해줄것이다.

중요: 원 주위에 chords의 나열을 조심스럽게 그리자. 각 chord의 길이는 "A"이다.

50cm dome을 위해서 A값은 15.45 cm 이다. 원 주위에 10개의 chord가 완벽하게 들어 맞도록 위치시키자.

이 라인들은 각 삼각형이 어디에 위치해야하는 지를 알려준다.

두개의 pentagon 사이에 하나의 A-A-A 삼각형을 붙여서 두개의 pentagon을 붙이자.

또 다른 삼각형은 다음과 같이 추가하자.

이 완성된 부분의 바닥 부분에 접착제를 붙이고, chords의 한 부분에 각 삼각형의 한 면을 위치시키자.

계속해서 pentagon과 삼각형을 추가하고, 접착제로 이들은 고정시키자.

equilateral ( A - A - A ) 삼각형은 맨 꼭대기의 pentagon 사이사이에 붙이자.

매 꼭대기에 마지막 pentagon을 붙이자.

여러분의 dome은 완성되었다. dome에 관한 것을 더 배우고 싶다면 다음의 링크를 따라가자. Dome Math.

이 페이지는 Hila Science Camp: http://hilaroad.com 에 의해서 만들어 졌습니다.

그리고 좀 더 복잡하고 실제적인 내용은 다음 링크를 따라가 보자. 다른 내용도 유용한 것들이 많다. - http://www.byexample.com/articles/topics/geodesic_domes